Preliminary

W99200F

# W99200F

# MPEG1 Video Encoder Data Sheet

**Rev 1.0**

CONFIDENTIAL

Publication Release Date: 1999/05/03 Revision 1.0

1

The information described in this document is the exclusive intellectual property of Winbond Electronics Corporation and shall not be reproduced without permission from Winbond.

Winbond is providing this document only for reference purposes of W99200F-based system design. Winbond assumes no responsibility for errors or omissions. All data and specifications are subject to change without notice.

WinMPEG is a registered trademark of Winbond Electronics. PC, AT and IBM are registered trademarks of International Business Machines, Inc. DOS and Windows are registered trademarks of Microsoft corporation. All other trademarks mentioned in this document are property of their respective owners.

For additional information or questions, please contact: Hung-Ming Wang

Multimedia Product Marketing & Planning Dept. TEL: 886-3-5790666 Ext. 6135 FAX: 886-3-5796139 Email : hmwang0@winbond.com.tw

Copyright 1999 (all rights reserved) Winbond Electronics Corporation Web: <u>http://www.winbond.com.tw</u>

This product is jointly developed with **Zapex Research Ltd.** Web: <u>http://www.zapex.co.il</u>

# CONFIDENTIAL

2

Preliminary

# **Table of Contents**

| 1. General Description                                   | 7  |

|----------------------------------------------------------|----|

| 2. Features                                              | 9  |

| 2.1 PCI Interface                                        |    |

| 2.2 Parallel Port Interface                              |    |

| 2.3 Generic Bus Interface                                |    |

| 2.4 VCD Decoder Interface                                | 9  |

| 2.5 Audio Bitstream Input Interface                      | 9  |

| 2.6 Live Video Encoding                                  |    |

| 2.7 Live Video Pass Through                              |    |

| 2.8 Live Video Snap Shot                                 |    |

| 2.9 Single Frame Encoding                                |    |

| 2.10 Write / Read a frame                                |    |

| 2.11 Write / Read from / to SDRAM                        |    |

| 2.12 Write / Read from /to internal memories             |    |

| 2.13 System Consideration                                |    |

| 2.14 Technology                                          |    |

| 3. Pin Configuration                                     | 14 |

| 4. Pin Description                                       | 15 |

| 4.1 Miscellaneous and System Operation Signals (42 pins) |    |

| 4.2 Host Bus Signals (50 pins)                           |    |

| 4.3 DRAM Interface Signals (33 pins)                     |    |

| 4.4 Video Decoder Interface Signals (14 pins)            |    |

| 4.5 I <sup>2</sup> C Interface Signals (2 pins)          |    |

| 4.6 Decoder Interface Signals (13 pins)                  |    |

| 4.7 Audio Data Interface Signals (6 pins)                |    |

| 5. System Diagram                                        | 19 |

| 6. Block Diagram                                         |    |

| 6.1 Video pre processing                                 |    |

| 6.2 Memory (SDRAM) Interface                             |    |

| 6.3 Motion Estimation unit                               |    |

| 6.4 Motion Compensation                                  |    |

| 6.5 DCT/Q/iQ/iDCT                                        |    |

| 6.6 Variable Length Coding                               |    |

| 6.7 Control Unit                                         |    |

| 6.8 Rate Control Processor                               |    |

| 6.9 Generic Bus Interface                                |    |

| 6.10 Host Bridge                                         |    |

| 7. Functional Description                                | 24 |

| 7.1 Host Bus Interface                                   |    |

| 7.2 VCD Decoder Interface                                |    |

| 7.3 Audio Data Input Interface (AIN)                     |    |

| 7.4 Video Decoder Interface                              |    |

| 7.5 I <sup>2</sup> C interface                           |    |

| 7.6 Audio & Video synchronization                        | 57 |

# Preliminary

| 7.7 W99200F support for A/V synchronization by the System-Mux |  |

|---------------------------------------------------------------|--|

| 7.8 Reset                                                     |  |

| 7.9 Initialization                                            |  |

| 7.10 Operation Modes                                          |  |

| 7.11 Dealing with interrupt sources                           |  |

| 8. Control And Status Registers                               |  |

| 9. Electrical Characteristics                                 |  |

| 9.1 Absolute Maximum Rating                                   |  |

| 9.2 DC Characteristics                                        |  |

| 9.3 AC Characteristics                                        |  |

| 10. Package Specification                                     |  |

|                                                               |  |

# **Table of Figures**

| Figure 1-1: A video encoding system based on the W99200F chip                  |     |

|--------------------------------------------------------------------------------|-----|

| Figure 3-1: Pin Out                                                            | 14  |

| Figure 5-1: W99200F A/V system                                                 | 19  |

| Figure 5-2: W99200F video system                                               | 20  |

| Figure 6-1: W99200F block diagram                                              | 21  |

| Figure 7-1: Layout of PCI Configuration                                        | 25  |

| Figure 7-2: PCI Configuration Read Timing                                      | 28  |

| Figure 7-3: PCI Configuration Write Timing                                     | 29  |

| Figure 7-4: PCI I/O Read Timing                                                | 30  |

| Figure 7-5: PCI I/O Write Timing                                               |     |

| Figure 7-6: PCI Target Mode Memory Read Timing                                 | 31  |

| Figure 7-7: PCI Memory Write Timing of Bus Master in Burst Mode                | 32  |

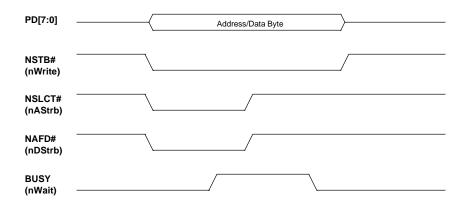

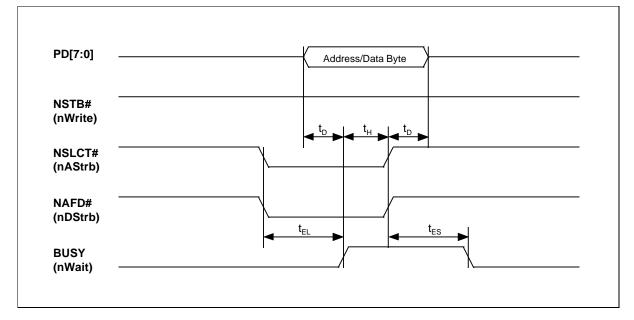

| Figure 7-8: Standard Parallel Port (SPP) Timing                                | 36  |

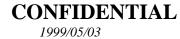

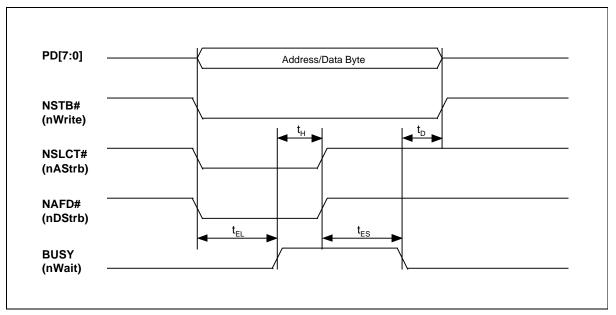

| Figure 7-9: EPP Data or Address Read Timing                                    | 37  |

| Figure 7-10: EPP Data or Address Write Timing                                  | 37  |

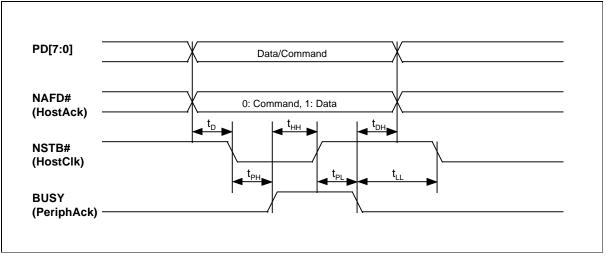

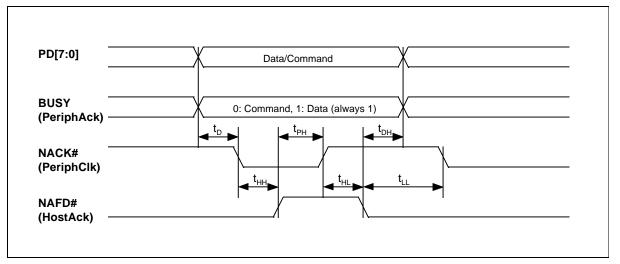

| Figure 7-11: ECP Forward Timing                                                | 38  |

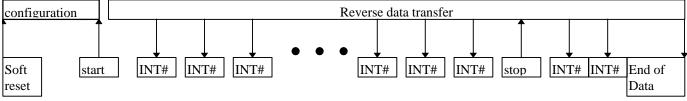

| Figure 7-12: ECP Reverse Timing                                                | 39  |

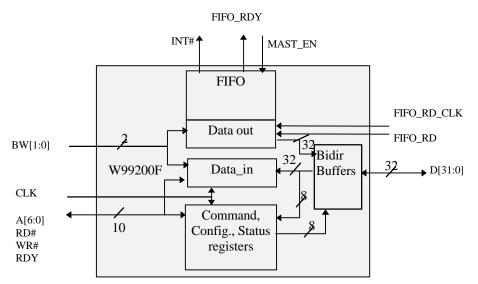

| Figure 7-13: Generic bus signals                                               | 40  |

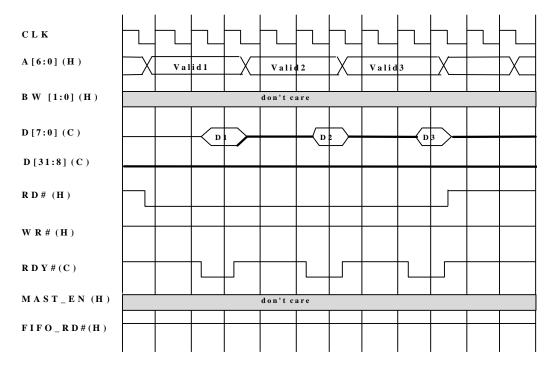

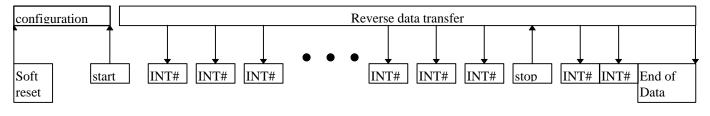

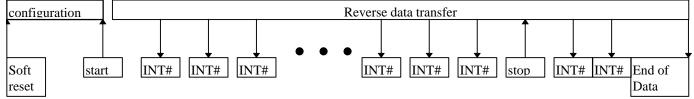

| Figure 7-14: Read cycles from configuration and status registers               |     |

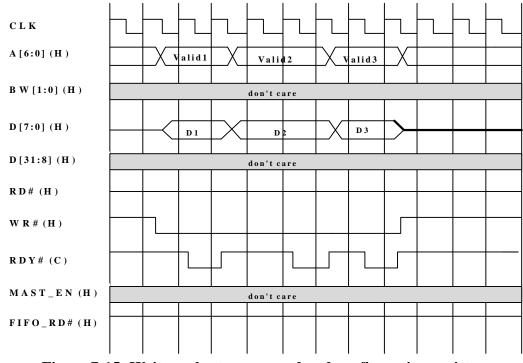

| Figure 7-15: Write cycles to command and configuration registers               | 41  |

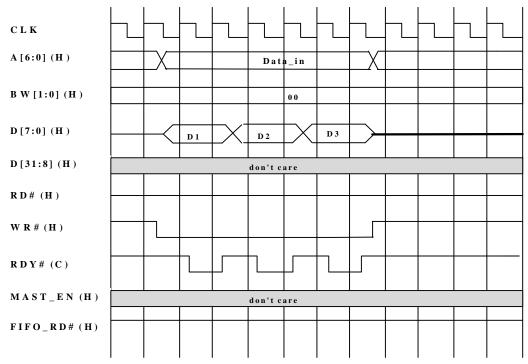

| Figure 7-16: Write cycles to Vdata_in register, BW[1:0]=00                     |     |

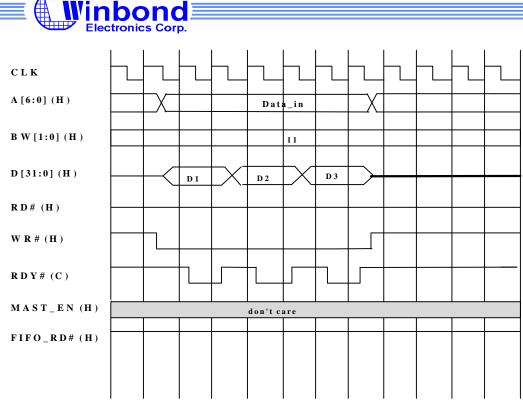

| Figure 7-17: Write cycles to Vdata_in register, BW[1:0]=11                     |     |

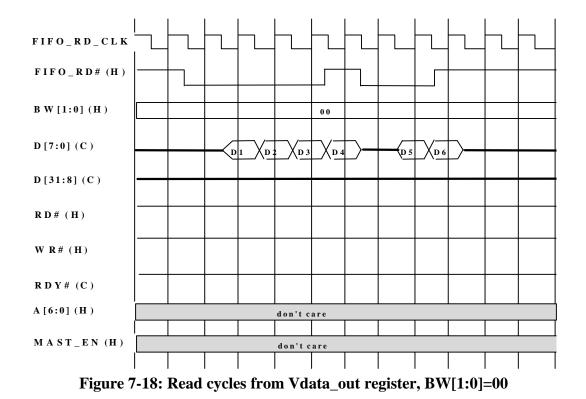

| Figure 7-18: Read cycles from Vdata_out register, BW[1:0]=00                   |     |

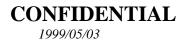

| Figure 7-19: FIFO_RDY and Read cycles from Vdata_out register, BW[1:0]=11      |     |

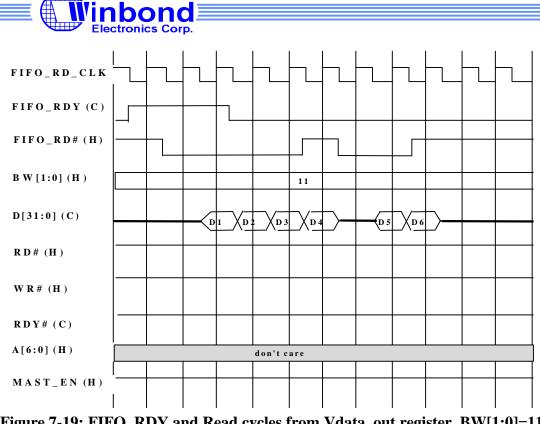

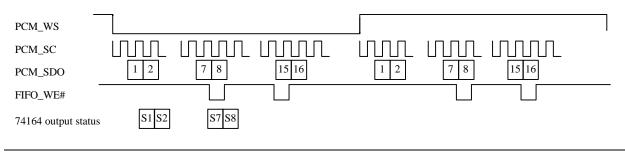

| Figure 7-20: I2S Format                                                        |     |

| Figure 7-21: Parallel FIFO Data Interface                                      |     |

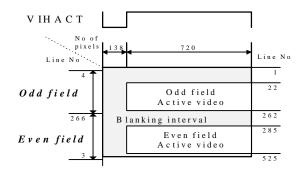

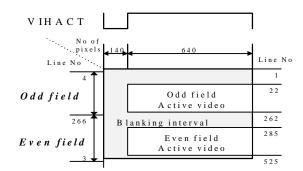

| Figure 7-22: Active video for ITU-R BT.601, NTSC                               |     |

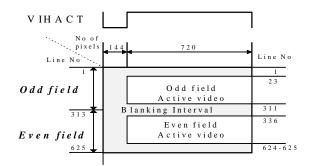

| Figure 7-23: Active video for ITU-R BT.601, PAL.                               |     |

| Figure 7-24: Active video for SQUARE, NTSC                                     |     |

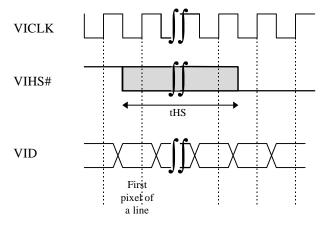

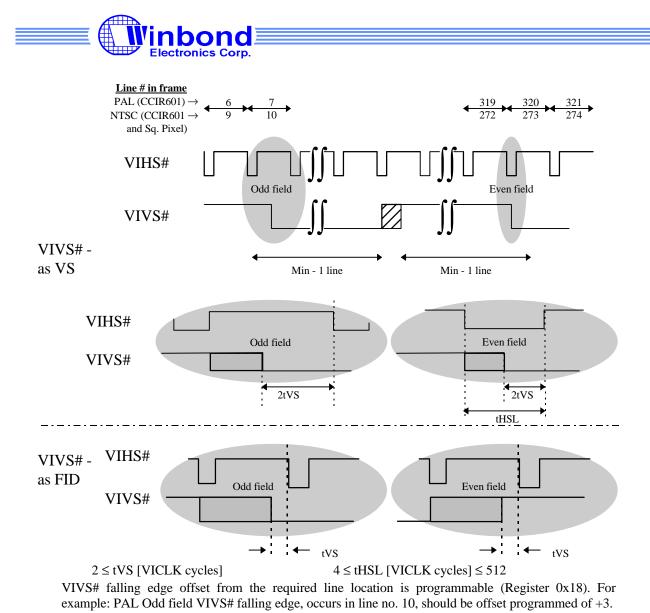

| Figure 7-25: VIHS# falling edge timing                                         |     |

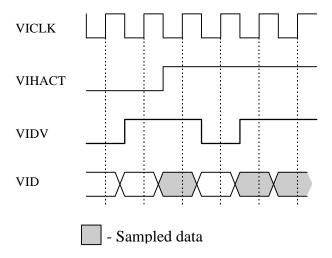

| Figure 7-26: VID sampling with VIDV                                            |     |

| Figure 7-27: video timing signals                                              |     |

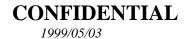

| Figure 7-28: CLK and RESET# after power up                                     |     |

| Figure 7-29: Sequence information in picture user data                         |     |

| Figure 7-30: Bit map divided to MBs                                            |     |

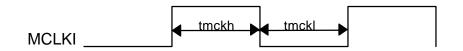

| Figure 9-1: System Clock Input Timing                                          |     |

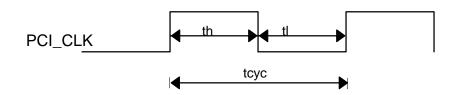

| Figure 9-2: PCI Clock Input Timing                                             |     |

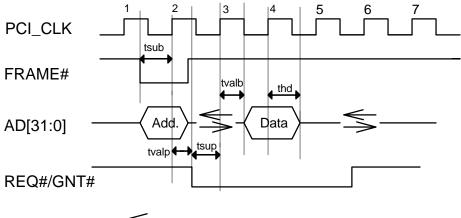

| Figure 9-3: PCI Operation                                                      |     |

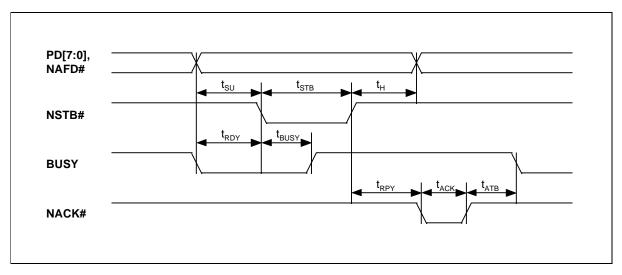

| Figure 9-4: Standard Parallel Port (SPP) Timing                                |     |

| Figure 9-5: EPP Data or Address Read Timing                                    |     |

| Figure 9-6: EPP Data of Address Write Timing                                   |     |

| Figure 9-0. EFF Data of Address write Timing<br>Figure 9-7: ECP Forward Timing |     |

| Figure 9-7: ECF Forward Timing                                                 |     |

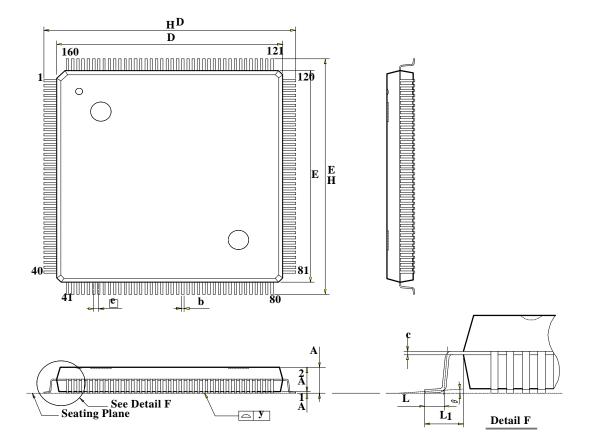

| Figure 9-8: ECF Reverse Timing<br>Figure 10-1: Package Specification           |     |

| rigure 10-1; rackage specification                                             | 110 |

# **Table of Tables**

| Table 2-1 : Input and output live video formats                        | 10  |

|------------------------------------------------------------------------|-----|

| Table 2-2: Decimation FIR filter                                       |     |

| Table 2-3: supported GOP structures                                    | 10  |

| Table 2-4: supported bit rate range                                    |     |

| Table 2-5: motion estimation algorithm and search window               | 11  |

| Table 6-1: Full-pel motion estimation algorithm and search window      |     |

| Table 7-1: Command Register Bits                                       |     |

| Table 7-2: Status Register Bits                                        |     |

| Table 7-3: Parallel Port Signals                                       |     |

| Table 7-4: Parallel Port Communication Modes                           |     |

| Table 7-5: Parallel Port Read/Write Signals                            |     |

| Table 7-6: Generic Bus Read and Write Signals from Internal Registers  | 39  |

| Table 7-7: Supported input video resolutions                           |     |

| Table 7-8: Video Input interface - Pin Description                     |     |

| Table 7-9: Video input programmable parameters                         | 50  |

| Table 7-10: I <sup>2</sup> C commands                                  |     |

| Table 7-11: Configuration registers in live MPEG1 encoding             | 64  |

| Table 7-12: Configuration registers in live M-JPEG encoding            |     |

| Table 7-13: User data format in VCD 2.0                                |     |

| Table 7-14: User data format in W99200F                                |     |

| Table 7-15: Configuration registers in live video pass through         | 68  |

| Table 7-16: Number of bytes per frame in Live video pass through       |     |

| Table 7-17: Configuration registers in live video snap shot            |     |

| Table 7-18: Configuration registers in Single frame encoding           |     |

| Table 7-19: Configuration registers in Write frame mode                |     |

| Table 7-20: Configuration registers in Read frame mode                 |     |

| Table 7-21: Configuration registers in SDRAM write mode                |     |

| Table 7-22: Configuration registers in SDRAM write mode                |     |

| Table 7-23: Configuration registers in SDRAM write mode                |     |

| Table 7-24: Configuration registers in Audio bitstreams input mode     |     |

| Table 7-25: Configuration sequence in VCD bitstreams pass through mode |     |

| Table 8-1: W99200F registers                                           |     |

| Table 9-1: Absolute Maximum Rating                                     | 111 |

| Table 9-2: DC Characteristics                                          | 111 |

| Table 9-3: System Clock Input Timing                                   |     |

| Table 9-4: PCI Clock Input Timing                                      | 112 |

| Table 9-5: PCI Operation Timing                                        |     |

| Table 9-6: Standard Parallel Port (SPP) Timing                         | 113 |

| Table 9-7: EPP Timing                                                  | 115 |

| Table 9-8: ECP Timing                                                  | 116 |

| Table 9-9: Generic Bus Timing                                          |     |

| Table 9-10: SDRAM Interface Timing                                     | 116 |

| Table 9-11: Video Decoder Interface Timing                             | 117 |

|                                                                        |     |

# 1. General Description

The W99200F is a **real time** MPEG1 / Motion JPEG video encoder. It can encode QSIF and SIF resolution pictures in a maximum picture rate of 30 pictures/sec.

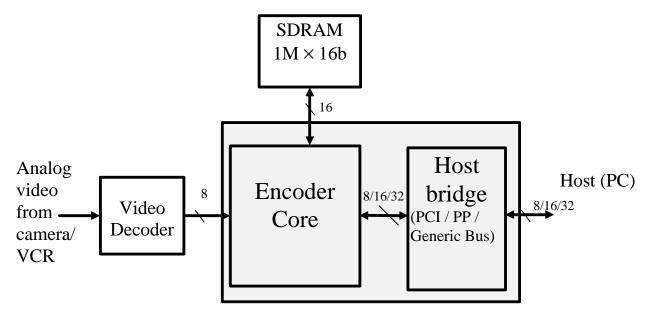

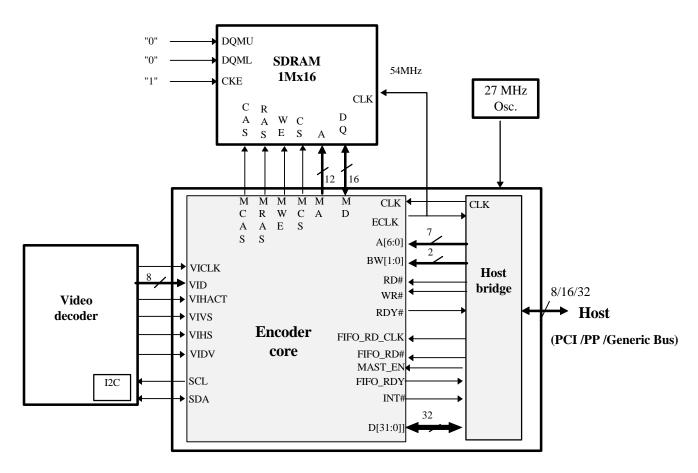

Figure 1-1 shows a typical system configuration based on the W99200F. This system can be used to capture analog video (from handycam or VCR), to encode it in MPEG1 or M-JPEG and to send it to a host. The host bridge directly provides signals for PCI bus, parallel port or generic bus without any glue logic outside the chip. The only memory component needed is a single  $1M \times 16$  bit SDRAM (that serves both as a frame buffer and as an external FIFO). The W99200F includes a glueless interface to popular video decoder devices. Thus, with only three components (W99200F, SDRAM and a video decoder) a complete MPEG1 video capturing and encoding system can be built.

Figure 1-1: A video encoding system based on the W99200F chip

The W99200F has ten modes of operations:

- 1. **Real time live video encoding**. In this mode the W99200F gets the live video from the video decoder, decimates it, encodes it in MPEG1 or JPEG formats and sends it to the host. Frame sizes supported are: SIF and QSIF.

- 2. **Real time live video pass through**. In this mode the W99200F gets the live video from the video decoder, decimates it and sends it to the host as YCbCr 4:2:0 video stream. Frame sizes supported are: SIF and QSIF. Frame rate is selectable from full rate (25/30 frames/seconds) down to one frame per two seconds.

- 3. Live video snap shot. In this mode the W99200F captures a single frame from the incoming live video and stores it into the SDRAM. The frame is filtered by adaptive filter in order to de-interlace it. Frame sizes supported are: FULL (YCbCr 4:2:0), SIF and QSIF.

- 4. **Single frame encoding**. In this mode the W99200F encodes picture already stored in the SDRAM as a MPEG1 I frame or as a JPEG frame and sends it to the host. Frame sizes in this mode are: every size from 32x32 pixels up to 720×576 pixels in a resolution of 16×16 pixels (MB).

CONFIDENTIAL

7

- 5. Write frame mode. In this mode the host can write a single frame in YCbCr 4:2:0 format to the SDRAM. Frame sizes in this mode are: every size from 32x32 pixels up to 720×576 pixels in a resolution of 16×16 pixels (MB).

- 6. **Read frame mode**. In this mode the host can read a single frame already stored in the SDRAM in YCbCr 4:2:0 format. Frame sizes in this mode are: every size from 32x32 pixels up to 720×576 pixels in a resolution of 16×16 pixels (MB).

- 7. **SDRAM write mode**. In this mode the W99200F enables the host to write any data to the SDRAM. The W99200F is only used as a bridge between the host and the SDRAM.

- 8. **SDRAM read mode**. In this mode the W99200F enables the host to read any data from the SDRAM. The W99200F is only used as a bridge between the host and the SDRAM.

- 9. Write internal memories mode. In this mode the W99200F enables writing to internal RAMs and registers. This is done in order to increase the encoder controllability and programmability.

- 10. **Read internal memories mode**. In this mode the W99200F enables reading of internal RAMs/ROMs and registers. This is done in order to increase the encoder observability.

Pay attention that by:

- activating modes 3+4 above the W99200F enables the host to capture a single frame from a live video in MPEG1 or JPEG formats.

- Activating modes 3+6 above the W99200F enables the host to capture a single frame from a live video in an uncompressed (YCbCr 4:2:0) format.

- Activating modes 5+4 above the W99200F enables the host to send uncompressed frame and get it back compressed.

The W99200F produces high quality MPEG1 / M-JPEG video by including a unique rate control algorithm and a dedicated hardware for most of the compression parts such as:

- High quality decimation filters.

- Half-pel accuracy motion estimation with a large search window. Distance between anchor frames ('m') up to 4.

- High precision DCT + Quantization.

- Entropy encoding.

- Automatic 3:2 and scene change detection.

In addition, W99200F Supports two interfaces:

- 1. Supports the VCD decoder interface (8051-like) to provide the function that VCD bitstreams can be sent from Generic bus, PCI or Parallel port host and pass through W99200F to VCD decoder.

- 2. Supports audio data input interface to provide the function that audio PCM data or compressed bitstreams can pass through W99200F and be sent to the host. There are two modes:

- without external audio FIFO: 3-pins Serial data interface.

- with external audio FIFO: 8-bits parallel FIFO data interface.

# CONFIDENTIAL

# 2. Features

# 2.1 PCI Interface

- 32-bit PCI bus interface which supports bus target mode and bus master mode write cycle for high bit rate output.

- provides a set of configuration registers to achieve the purpose of totally software initialization and configuration.

- programs encoder configuration registers and receives encoder status.

- output compressed bitstreams to host.

- monitors the input frames before and during encoding.

- operates up to 33 MHz.

# 2.2 Parallel Port Interface

- Supports Plug & Play using Nibble mode reverse channel transfer.

- Supports industrial standard SPP/EPP/ECP interface for configuration register programming and encoder status receiving.

- Supports industrial standard EPP/ECP interface for reverse data transfer to host.

- output compressed bitstreams to host.

- Monitors the selected input frames before and during encoding.

### 2.3 Generic Bus Interface

- Supports 32-bit bus interface.

- programs encoder configuration registers and receives encoder status.

- operates up to 54 MHz.

### 2.4 VCD Decoder Interface

- Support the VCD decoder interface (8051-like) to provide the function that VCD bitstreams can be sent from PCI or Parallel port host and pass through W99200F to VCD decoder.

- Glueless interface between W99200F and VCD decoder.

- W99200F and VCD decoder share the single 16M bits SDRAM.

#### 2.5 Audio Bitstream Input Interface

• Supports audio data input interface to provide the function that audio PCM data or compressed bitstreams can pass through W99200F and be sent to PC.

CONFIDENTIAL

- Mode I: without external audio FIFO. Support I2S interface to get bitstreams. Glueless interface between audio codec and W99200F.

- Mode II: with external audio FIFO. Support 8-bits parallel FIFO data interface. The size of external FIFO can be up to 256K bytes.

# 2.6 Live Video Encoding

- Real time (29.97-NTSC, 25-PAL) frames/seconds IBP MPEG1 encoder.

- Real time (29.97-NTSC, 25-PAL) frames/seconds M-JPEG encoder

- Encoding in SIF and QSIF resolutions.

- Video input format is selectable to one of: CCIR601 NTSC, CCIR601 PAL and SQUARE NTSC. Cropping and decimation are done according to the output formats (See Table 2-1).

|    | Input        | Input      | Output Video Resolution (4:2:0) |           |            |           |            |

|----|--------------|------------|---------------------------------|-----------|------------|-----------|------------|

|    | Video        | Video      | FULL                            |           | SIF        | QS        | SIF        |

|    | Format       | Resolution | Cropping                        | Cropping  | Decimation | Cropping  | Decimation |

| 1. | CCIR601 NTSC | 720 x 480  | 704 x 480                       | 704 x 480 | 352 x 240  | 704 x 448 | 176 x 112  |

| 2. | CCIR601 PAL  | 720 x 576  | 704 x 576                       | 704 x 576 | 352 x 288  | 704 x 576 | 176 x 144  |

| 3. | SQUARE NTSC  | 640 x 480  | -                               | -         | 320 x 240  | 640 x 448 | 160 x 112  |

| Table 2-1 | : Input and | output live | video formats |

|-----------|-------------|-------------|---------------|

|-----------|-------------|-------------|---------------|

• Decimation filters are

|      | Luminance             |                                                       | Chrom                 | inance                                                |

|------|-----------------------|-------------------------------------------------------|-----------------------|-------------------------------------------------------|

|      | Horizontal Vertical   |                                                       | Horizontal            | Vertical                                              |

| FULL | -                     | adaptive field<br>averaging                           | -                     | adaptive field<br>averaging + 2 tap 2:1<br>decimation |

| SIF  | 17 tap 2:1 decimation | adaptive field<br>averaging + 3 tap 2:1<br>decimation | 10 tap 2:1 decimation | drop field + 10 tap 2:1<br>decimation                 |

| QSIF | 21 tap 4:1 decimation | drop field + 17-tap 2:1<br>decimation                 | 9 tap 4:1 decimation  | drop field + 9-tap 4:1<br>decimation                  |

#### Table 2-2: Decimation FIR filter

• Supports I, P and B frames and a programmable GOP structure (m and n values):

| m | n            | Frame Sequence   | Comments                       |

|---|--------------|------------------|--------------------------------|

| 1 | 1            | IIIIIIIII        |                                |

| 1 | 2 <= n <=60  | IPPPPPI          |                                |

| 2 | 2            | BIBIBIBIBI       |                                |

| 2 | 2 <= n <=60  | BIBPBPBPBI       | n grows in steps of 2: 2,4,,60 |

| 3 | 3 <= n <= 60 | BBIBBPBBPBBI     | n grows in steps of 3: 3,6,,60 |

| 4 | 4 <= n <= 60 | BBBIBBBPBBBPBBBI | n grows in steps of 4: 4,8,,60 |

Table 2-3: supported GOP structures

CONFIDENTIAL 1999/05/03

• Bit rate is selected via the host interface. Supported bit rate range (in steps of 400 bits/second):

| Frame size | MPGE1 "I" frame (bits/second) | MPEG1 "IBP" (bits/second) |

|------------|-------------------------------|---------------------------|

| SIF        | 1.5 M - 9.0 M                 | 192 K - 6.0 M             |

| QSIF       | 0.5 M - 3.0 M                 | 64 K- 2 .0 M              |

#### Table 2-4: supported bit rate range

- Three bit rate policies are supported for MPEG1 encoding:

- Constant bit rate: stuffing included when needed.

- Maximum bit rate: no stuffing.

- Variable bit rate: constant quality.

Note: For M-JPEG encoding, only the last policy (variable bit rate) is supported.

• An on chip motion estimation unit to support a Search Window (SW) with Half Pixel accuracy. SW sizes:

|                             |         | SIF                   | QSIF                  |

|-----------------------------|---------|-----------------------|-----------------------|

| Search Technique (full-pel) |         | 2 stage logarithmic   | Exhaustive            |

| Search Window               | P frame | ±41.5 (H) - ±19.5 (V) | ±31.5 (H) - ±15.5 (V) |

|                             | B frame | ±25.5 (H) - ±15.5 (V) | ±15.5 (H) - ±15.5 (V) |

#### Table 2-5: motion estimation algorithm and search window

- Automatic Inverse Telecine for 29.97 frames/second video input (Optional).

- Automatic scene change control (Optional.)

- Automatic time code generation, initial value programmed by the host. Drop Frame Flag is supported for 29.97 frames/seconds video.

- Insertion of a user defined bit-map into the encoded video with two level alpha-blending (Optional).

- Insertion of Time-stamp into the MPEG1 bit-stream (Optional).

- Skipping B-frames by repeating last P-frame for low-bitrate encoding (Optional).

- Host selectable encoding parameters:

- Encoding picture size: SIF/QSIF

- Encoding Format: MPEG1 / M-JPEG

- Bit rate policy: constant, maximum, variable.

- ♦ GOP structure: m, n.

- Half pixel control: on/off.

- B start sequence: on/off.

- Open/Close GOP.

- Inverse telecine control: on/off.

- Scene change control: on/off

- Initial time code.

- Headers frequency: Sequence header, GOP header, Slice header.

- VBV size and initial fullness.

### CONFIDENTIAL

1999/05/03

11

- Status:

- FIFO status

- Video decoder status

- Encoding status (available once per frame):

Frame time code.

Frame type: I,B,P.

Frame bit budget

VBV level.

First frame in a new scene.

### 2.7 Live Video Pass Through

- Passes YCbCr 4:2:0 video from the video decoder to the host

- Frame resolution supported are SIF and QSIF.

- Cropping and decimation according to Table 2-1.

- Frame rate selectable by the host.

- Insertion of a user defined bit-map into the incoming video with two level alpha-blending (Optional).

### 2.8 Live Video Snap Shot

- Capture a single frame from the video decoder on the SDRAM in YCbCr 4:2:0 format.

- Frame resolution supported are FULL, SIF and QSIF.

- Cropping and decimation according to Table 2-1.

- Insertion of a user defined bit-map into the incoming video with two level alpha-blending (Optional).

### 2.9 Single Frame Encoding

- Encoding single picture in MPEG1 I frame or in JPEG.

- Source picture stored on the SDRAM as YCbCr 4:2:0 in any resolution which is aligned to MB borders from 2 × 2 MBs (32 × 32 pixels) up to 45 × 36 MBs (720 × 576 pixels).

- Encoded picture in the same resolution as the input picture.

### 2.10 Write / Read a frame

- A frame previously stored in the SDRAM (e.g., by Live Video Snap Shot) can be read out to the host in YCbCr format.

- The host can write a frame into the SDRAM in YCbCr format. This frame can be encoded later on by using single frame encoding mode.

# 2.11 Write / Read from / to SDRAM

• The W99200F enables the host to write/read any data to/from the SDRAM. This may serve the system to enlarge its memory.

# 2.12 Write / Read from /to internal memories

• The W99200F enables the host to write/read part of its internal memories. This is done in order to enable future modifications to the encoder and by that increases its programmability.

# 2.13 System Consideration

- Glueless interface to popular video decoders. Host can program the video decoder interface.

- I<sup>2</sup>C protocol supported for programming the video decoder.

- Automatic detection of "stop" condition in the incoming video (time-out on the video decoder "sync" signals).

- Only one component of memory is needed:  $1M \times 16$  bit SDRAM . 256K Bytes (256K  $\times$  8 bit) video FIFO is implemented in the SDRAM.

- W99200F program size is 1536 bytes, to be loaded by the system host at initial configuration time.

- Minimum latency from the incoming video to the output bit stream.

- Perfect Audio/Video synchronization support by stream and by a special pin. PTS(Presentation Time Stamp) for stream support and OSYNC# pin for active video.

- provides programmable I/O pins for system control.

# 2.14 Technology

- 3.3 voltage operation

- Power consumption (Maximum) : 0.9 W

- Built-in power-saving mode

- Operating frequency: 54MHz

- 160-pin PQFP

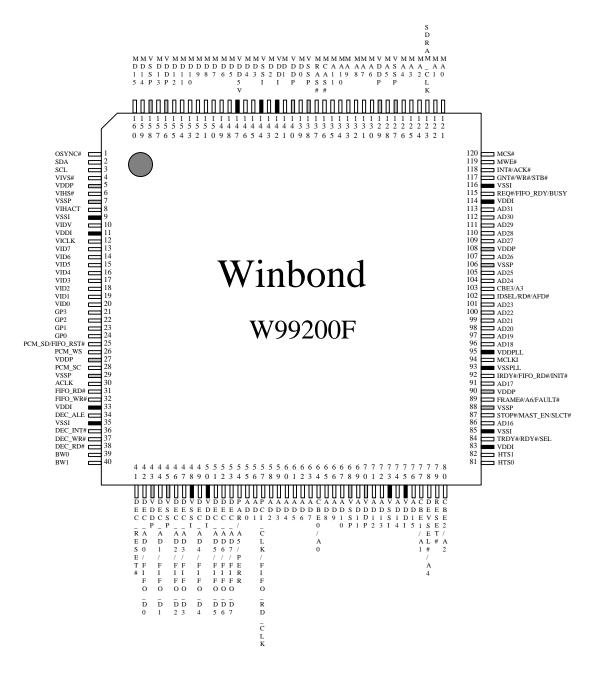

3. Pin Configuration

Figure 3-1: Pin Out

CONFIDENTIAL 1999/05/03

# 4. Pin Description

# 4.1 Miscellaneous and System Operation Signals (42 pins)

| pin name              | type | pin description                                                                                                                               |

|-----------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| MCLKI                 | Ι    | Main clock input. An appropriate choice for system operation is 27 MHz.<br>W99200F uses an internal PLL to generate main operating clock. The |

|                       |      | frequency of main operating clock is two times that of MCLKI.                                                                                 |

| HTS[1:0]              | I    | Host type select.                                                                                                                             |

|                       |      | 00, means 32-bit PCI bus is selected,                                                                                                         |

|                       |      | 01, means ECP/EPP parallel port is selected,                                                                                                  |

|                       |      | 10, means generic bus is selected,                                                                                                            |

|                       |      | 11, means test mode to tri-state all output signals.                                                                                          |

| GP[3:0]               | I/O  | Programmable general purpose input/output pins.                                                                                               |

| <b>VDD5V</b> (1)      |      | 5 voltage power supply.                                                                                                                       |

| VDDPLL (1)            |      | 4.1 voltage power supply for PLL circuit.                                                                                                     |

| VSSPLL (1)            |      | analog ground for PLL circuit.                                                                                                                |

| VDDI (7),<br>VDDP (9) |      | 3.3 voltage power supply                                                                                                                      |

| VSSI (7),<br>VSSP (9) |      | 0 voltage ground                                                                                                                              |

# 4.2 Host Bus Signals (50 pins)

| pin name    | type | pin description                                                       |

|-------------|------|-----------------------------------------------------------------------|

| RESET#      | I I  | System reset, active low.                                             |

| PCI CLK/    | I    |                                                                       |

| _           | 1    | In PCI bus, PCI bus clock, up to 33 MHz.                              |

| FIFO_RD_CLK |      | In Generic bus, fifo read clock, up to 54MHz.                         |

| AD[31:0]    | I/O  | In PCI bus, 32-bit multiplexed system address and data bus.           |

|             |      | In Generic bus, Data bus.                                             |

|             |      | In Parallel Port, AD[7:0] is used as PD[7:0], parallel port data bus. |

| FRAME#/     | I/O  | In PCI bus, Cycle Frame, active Low.                                  |

| A[6]/       |      | In Generic bus, address bus bit 6. Input only.                        |

| FAULT#      |      | In Parallel Port, fault, active low. Output only.                     |

| PAR/        | I/O  | In PCI bus, parity is even parity across address bus and CBE,         |

| A[5]/       |      | required by all PCI agents.                                           |

| PERR        |      | In Generic bus, address bus bit [5]. Input only.                      |

|             |      | In Parallel Port, paper error, active high. Output only.              |

| DEVSEL#/    | I/O  | In PCI bus, Device Select, active Low.                                |

| A[4]        |      | In Generic bus, address bus bit [4]. Input only.                      |

| CBE[3:0]/   | I/O  | In PCI bus, Bus Command and Byte Enable defines bus command           |

| A[3:0]      |      | and valid byte.                                                       |

|             |      | In Generic bus, address bus bits [3:0]. Input only.                   |

| TRDY#/      | I/O  | In PCI bus, Target Ready, active Low.                                 |

| RDY#/       |      | In Generic bus, access operation is finished, active low. Output      |

| SEL         |      | only.                                                                 |

# Preliminary

|           |     | In Parallel Port, select, active high. Output only.                |  |

|-----------|-----|--------------------------------------------------------------------|--|

| IRDY#/    | I/O | In PCI bus, Initiator Ready, active Low.                           |  |

| FIFO_RD#/ |     | In Generic bus, FIFO read signal, active low. Input only.          |  |

| INIT#     |     | In Parallel Port, initial, active low. Input only.                 |  |

| STOP#/    | I/O | In PCI bus, Transaction Vstop, active Low.                         |  |

| MAST_EN/  |     | In Generic bus, master mode enable. Enables bus ownership          |  |

| SLCT#     |     | request, active high. Input only.                                  |  |

|           |     | In Parallel Port, select in, active low. Input only.               |  |

| IDSEL/    | Ι   | In PCI bus, Initialization Device Select is used as chip select in |  |

| RD#/      |     | configuration transaction cycles. Active high.                     |  |

| AFD#      |     | In Generic bus, read enable, active low.                           |  |

|           |     | In Parallel Port, auto line feed, active low.                      |  |

| REQ#/     | 0   | In PCI bus, Bus Request indicates to the bus arbiter that the      |  |

| FIFO_RDY/ |     | W99200F requires the use of PCI bus. Active low.                   |  |

| BUSY      |     | In Generic bus, Fifo data is ready, active high.                   |  |

|           |     | In Parallel Port, not ready to receive data, active high.          |  |

| GNT#/     | Ι   | In PCI bus, Bus Grant indicates to the W99200F that the PCI bus    |  |

| WR#/      |     | is granted. Active low.                                            |  |

| STB#      |     | In Generic bus, write enable, active low.                          |  |

|           |     | In Parallel Port, strobe signal, active low.                       |  |

| INT#/     | 0   | In PCI and Generic bus, Interrupt Request. Active low.             |  |

| ACK#      |     | In Parallel Port, acknowledge, active low.                         |  |

| BW[1:0]   | Ι   | In Generic bus, Bus Width,                                         |  |

|           |     | 00: 8 bits,                                                        |  |

|           |     | 01: 16 bits,                                                       |  |

|           |     | 10: not used,                                                      |  |

|           |     | 11: 32 bits.                                                       |  |

# 4.3 DRAM Interface Signals (33 pins)

| pin name  | type | pin description                                                                                                                                    |  |

|-----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SDRAM_CLK | 0    | SDRAM clock. Its frequency is the twice of MCLKI. It can<br>programmably be tri-state. An appropriate frequency for system<br>operation is 54 MHz. |  |

| MA[11:0]  | 0    | SDRAM address bus. It can programmably be tri-state.                                                                                               |  |

| MD[15:0]  | I/O  | SDRAM data bus. It can programmably be tri-state.                                                                                                  |  |

| MCS#      | 0    | SDRAM chip select, active low. It can programmably be tri-state.                                                                                   |  |

| MRAS#     | 0    | SDRAM row address select, active low. It can programmably be tri-<br>state.                                                                        |  |

| MCAS#     | 0    | SDRAM column address select, active low. It can programmably be tri-<br>state.                                                                     |  |

| MWE#      | 0    | SDRAM write enable, active low. It can programmably be tri-state.                                                                                  |  |

# 4.4 Video Decoder Interface Signals (14 pins)

| pin name | type | pin description                                                      |

|----------|------|----------------------------------------------------------------------|

| VICLK    | Ι    | Video Input Clock. Free running clock. Allowed frequency: 24.54MHz - |

# CONFIDENTIAL

1999/05/03

|          |   | 36MHz.                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VID[7:0] | Ι | Video Input Data. VID[7:0] for Y/Cb/Cr[7:0].                                                                                                                                                                                                                                                                                                                                                     |

| VIDV     | I | Video Input Data Valid. Pixel data is sampled only if this signal is high (default). Polarity is programmable via register 0x19.                                                                                                                                                                                                                                                                 |

| VIHACT   | I | Video Input Horizontal Active pixels identifier. When high (default) indicates the active period of a video line. During VBI there may be an activation of this signal. However, No pixel data is sampled during a VBI window. When active during an active video line, pixel data is sampled with every rising edge of VICLK, where VIDV is active. Polarity is programmable via register 0x19. |

| VIHS#    | I | Video Input Horizontal Sync signal. Falling edge (Default) indicates a new line. Signal polarity is programmable via register 0x19.                                                                                                                                                                                                                                                              |

| VIVS#    | Ι | Video Input Vertical Sync signal. Falling edge (default) indicates a new field. Signal polarity and line offset are programmable via registers 0x18 and 0x19.                                                                                                                                                                                                                                    |

| OSYNC#   | 0 | Video Out of Sync signal. It is used to indicate the input video data is out<br>of sync. While it is active, system should stop to latch audio data. Active<br>low.                                                                                                                                                                                                                              |

# 4.5 I<sup>2</sup>C Interface Signals (2 pins)

| pin name | type | pin description        |

|----------|------|------------------------|

| SCL      | I/O  | I <sup>2</sup> C clock |

| SDA      | I/O  | I <sup>2</sup> C data  |

# 4.6 Decoder Interface Signals (13 pins)

| pin name     | type | pin description                                                    |

|--------------|------|--------------------------------------------------------------------|

| DEC_RESET#   | 0    | Decoder reset signal, active low.                                  |

| DEC_AD[7:0]/ | I/O  | In decoding mode, they are used for decoder address/data bus.      |

| FIFO_D[7:0]  |      | Output for multiplexed 8-bit address bus and data bus.             |

|              |      | Input for 8-bit data bus.                                          |

|              |      | In encoding mode, they are FIFO parallel data input.               |

| DEC_ALE      | 0    | Decoder address latch enable for 8051-series uP, active high.      |

| DEC_RD#      | 0    | Decoder read enable, active low.                                   |

| DEC_WR#      | 0    | Decoder write enable, active low.                                  |

| DEC_INT#     | Ι    | Decoder interrupt request input, active when an interrupt event is |

|              |      | triggered, active low.                                             |

# 4.7 Audio Data Interface Signals (6 pins)

1999/05/03

| р | in name | type  | pin description |    |                           |

|---|---------|-------|-----------------|----|---------------------------|

|   | CONFIDE | NTIAI | 4               | 17 | Publication Release Date: |

| ACLK      | I   | Audio master clock. Its frequency is programmable. The frequency should be the multiple of 44.1KHz. The default frequency is 11.2896MHz. It is used to generate PCM_SC and PCM_WS signals. |  |

|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PCM_SC    | 0   | Audio codec clock.                                                                                                                                                                         |  |

| PCM_WS    | 0   | Audio codec clock.                                                                                                                                                                         |  |

| PCM_SD/   | I/O | In I <sup>2</sup> S interface mode, serial data. Input.                                                                                                                                    |  |

| FIFO_RST# |     | In FIFO interface mode, it is used to reset FIFO. Active low. Output.                                                                                                                      |  |

| FIFO_RD#  | 0   | In I <sup>2</sup> S interface mode, it is not used.                                                                                                                                        |  |

|           |     | In FIFO interface mode, FIFO read enable. Active low.                                                                                                                                      |  |

| FIFO_WR#  | 0   | In I <sup>2</sup> S interface mode, it is not used.                                                                                                                                        |  |

|           |     | In FIFO interface mode, FIFO write enable. Active low.                                                                                                                                     |  |

# 5. System Diagram

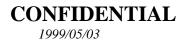

W99200F is a single-chip real time MPEG-1 and Motion JPEG Video Encoder for low-cost PC-based video capture and encoding. It is companioned with software MPEG-1 audio encoder, A/V mixing and authoring tools. It has two kinds of H/W configuration: (1) external box with connection to PC parallel port, (2) PCI add-on card. It provides modes of Preview, Real-time encode, Monitoring and I-frame Edit.

Figure 5-1 shows a complete video encoding/decoding system. This system contains the following parts:

- 1. W99200F.

- 2. Video decoder chip.

- 3. VCD decoder chip. (Glueless interface to Winbond W9925QF and W9926QF.)

- 4. Audio codec.

- 5. TV encoder.

- 6. One 1M x 16 bit SDRAM component. This SDRAM is shared by W99200F and VCD decoder.

Figure 5-1: W99200F A/V system

**CONFIDENTIAL** 1999/05/03

Figure 5-2 shows a simple PC based capturing and encoding system which is based on the W99200F. Such a system contains the following parts:

- 1. W99200F

- 2. Video decoder chip that captures the analog live video from the camera or VCR and converts it to a digital YCbCr 4:2:2 bit stream (glueless interface to popular video decoders, such as: Philips SAA7110/11/12/13/14, BrookTree Bt827/9, Samsung KSO122/127, etc.).

- 3. One  $1M \times 16b$  SDRAM component. This SDRAM is used as a frames buffer and as the video bit stream FIFO.

Figure 5-2: W99200F video system

# 6. Block Diagram

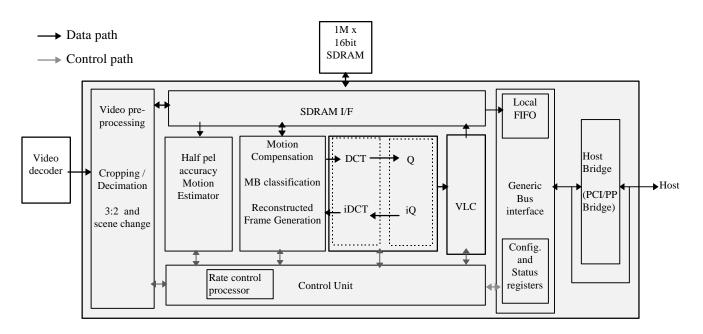

This chapter describes the functionality of the main units of the W99200F. Figure 6-1 shows the block diagram of the W99200F. The following sections describe the functionality of each block.

Figure 6-1: W99200F block diagram

### 6.1 Video pre processing

The video input interface is responsible for the following three major activities:

- Decimation and cropping.

- Telecine detection.

- Scene change detection.

#### 6.1.1 CCIR to SIF Decimation.

This block gets the 4:2:2 video input from the video decoder and performs decimation to the requested frame size according to Table 2-2.

#### 6.1.2 Telecine Detection

MPEG-1 provides means to encode film originated NTSC video stream by specifying the frame rate in the Video Sequence header. The W99200F detects an NTSC video stream generated by a 3:2 pulldown process, and convert it back into film rate stream, dropping the redundant fields. In that case the W99200F indicates a 23.976 frame/sec rate in the Video Sequence header.

Publication Release Date:

21

#### 6.1.3 Scene Change Detection

A video stream may have scene changes within. An ordinary scene change is associated with a significant difference between the last frame of the previous scene and the first frame of the new scene. The W99200F detects that difference, and recommends to encode the new scene's first as a first frame of a new group of pictures (either an I frame or a "closed GOP" B frame), thus improving the encoded video quality.

### 6.2 Memory (SDRAM) Interface

SDRAM interface block is responsible to the write and read transactions to the SDRAM as well as refresh cycles. It does not arbitrate the SDRAM accesses (priority determination), but rather translates read and write commands with its addresses to SDRAM legal sequences.

#### 6.3 Motion Estimation unit

The Motion Estimation unit finds a Minimum SAD for every Template MB (TMB) in "P" and "B" frames. The Motion estimation works in full-pel and half-pel resolution. The full-pel search is done according to Table 6-1. The half-pel search is done on the eight half-pel vectors which surrounds the best full-pel motion vector.

|                  |         | SIF                 | QSIF              |

|------------------|---------|---------------------|-------------------|

| Search Technique |         | 2 stage logarithmic | Exhaustive        |

| Search Window    | P frame | ±41 (H) - ±19 (V)   | ±31 (H) - ±15 (V) |

|                  | B frame | ±25 (H) - ±15 (V)   | ±15 (H) - ±15 (V) |

#### Table 6-1: Full-pel motion estimation algorithm and search window

#### 6.4 Motion Compensation

Motion compensation block. This block performs the following tasks:

- Calculate the Intra SAD

- Calculate the interpolated SAD ("B" frame)

- Do the MB classification (fwd, bwd, itp, zero-motion, etc)

- Calculate the motion compensated MB: the differences between the original MB and its predictor ("P" and "B" frames), according to rate-control unit MB classification decision.

- Calculate the reconstructed frame ("I" and "P" frames). In SIF encoding calculate the reconstructed decimated (QSIF) Luma parts (for ME).

# 6.5 DCT/Q/iQ/iDCT

DCT/iDCT block performs the Discrete Cosine Transform and the inverse Transform. Q/iQ block performs the quantization and the inverse quantization according to the MPEG1 / M-JPEG standards.

### 6.6 Variable Length Coding

Variable Length Coding (VLC) block is responsible for the following:

1. Generate MPEG1 bit stream when encoding is MPEG1.

CONFIDENTIAL

1999/05/03

22

2. Generate M-JPEG bit stream when encoding is M-JPEG.

The produced bit stream is written into the SDRAM FIFO.

### 6.7 Control Unit

Control unit controls all W99200F activity. It is responsible for:

- 1. Synchronization between the different blocks.

- 2. Time code generation.

#### 6.8 Rate Control Processor

The rate control processor is responsible for controlling the Frame/MB bit budget to meet the required MPEG1 stream bit rate. There are three supported modes of operations:

- 1. Constant bit rate. The RCP is responsible for shuffling the bit budget among frames and MB according to complexity of the picture or a portion of a picture. It is responsible for the VBV control, zero stuffing, etc.

- 2. Maximum bit rate. The same as above, with no zero stuffing.

- 3. Constant quality. I.e., constant quantization factor. In that case there is no need to handle a VBV. Also, no stuffing is needed.

The Rate-control is also performs MB classification.

#### 6.9 Generic Bus Interface

Generic Bus Interface is the unit that performs the generic bus protocol and is connected to the host bridge. The generic bus interface also includes the local FIFO and the configuration and status registers.

#### 6.9.1 Local FIFO

Local FIFO is a small FIFO from which the output bit stream is read to the host port.

#### 6.9.2 Configuration and status registers

Through these registers the host controls the W99200F.

#### 6.10 Host Bridge

Host Bridge is the unit that decodes host bus signals and transfer host operation to generic bus signals. It includes PCI interface, parallel port interface, decoder interface and audio input interface.

# 7. Functional Description

# 7.1 Host Bus Interface

The host bus interface has built for interfacing with three kinds of host bus, which are:

- 1. 32-bit PCI bus

- 2. parallel port

- 3. generic bus

#### 7.1.1 32-bit PCI Bus

The PCI block provides an easy interface with PCI bus such that no extra bridge components are needed. The W99200F provides two operating modes in PCI bus: bus target and bus master. When acting as a bus target, the W99200F responds to I/O-mapped, memory-mapped and configuration access cycles. While playing the role of a bus master, the W99200F will issues the memory write command to move the bitstream data to system main memory. There are four types of access cycles, including:

- Configuration cycle,

- Target mode I/O read/write cycle,

- Target mode memory read cycle,

- Master mode memory write Cycle (Initiated by W99200F while it acts as a bus master).

#### 7.1.1.1 Configuration Cycle:

Based on the PCI 2.1 local bus definition, a set of configuration registers are built in the W99200F to achieve the purpose of total software initialization and configuration. The description of configuration registers which are used in the W99200F is given as followings:

| <u>31</u> <u>16 15</u> C |                                  |               |                | )   |  |

|--------------------------|----------------------------------|---------------|----------------|-----|--|

| Devi                     | ce ID                            | Vendor ID     |                | 00h |  |

| Statu                    | IS                               | Comn          | nand           | 04h |  |

|                          | Class Code                       |               | Revision ID    | 08h |  |

| BIST                     | Header Type                      | Latency Timer | Cash Line Size | 0Ch |  |

|                          |                                  |               |                | 10h |  |

|                          |                                  |               |                | 14h |  |

|                          |                                  |               |                | 18h |  |

|                          | Base Addre                       | ess Register  |                | 1Ch |  |

|                          |                                  |               |                |     |  |

|                          |                                  |               |                |     |  |

|                          | Cardbus                          | CIS Pointer   |                | 28h |  |

| Subs                     | Subsystem ID Subsystem Vendor ID |               |                |     |  |

|                          | Expansion ROM Base Address       |               |                |     |  |

| Reserved                 |                                  |               |                | 34h |  |

|                          | Reserved                         |               |                | 38h |  |

| Max_Lat                  |                                  |               |                | 3Ch |  |

| Figure 7-1: | Layout of PCI | Configuration |

|-------------|---------------|---------------|

|             | •             |               |

The following section is the description of each register in the configuration space.

- Vender ID : This field identifies the manufacturer of the device. It's a read-only register. For Winbond Electronics Corporation, the Vender ID is <u>1050h</u>.

- Device ID : This field identifies the particular device and it is read-only. For the W99200F, the Device ID is <u>9922h</u>.

- **Revision ID**: This field specifies a device specific revision identifier and it is read-only. The ID number of this revision is <u>03h</u>.

- **Header Type :** This byte identifies the layout of bytes 10h through 3Fh in configuration space and also whether or not the device contains multiple function. For the W99200F, bit 7 is set to 0 to specifies that the W99200F is single function. Bit[6:0] are set to 00h to specify that the layout of bytes 10h through 3Fh is as shown in Figure 7-1. This register is read-only.

- **Class Code :** This field is used to identify the generic function of device. This register is broken into three byte size field. The upper byte is a base class code, the middle is a sub-class code and the lower byte identifies a specific register-level programming interface. For the W99200F, the register is set to <u>040000h</u> to identify the W99200F is a Multimedia device. This is also a read-only register.

- **Command :** The Command register provides coarse control over the device's ability to generate and respond to PCI cycles. When a 0 is written into this register, the device is logically disconnected from the PCI bus for all accesses except configuration accesses. The definition of each bit in this register is given in Table 7-1.

- **Status :** The Status register is used to record status information for PCI bus related events. The definition of this register is given in Table 7-2. For this register, a bit is reset whenever the register is written and the written data in the corresponding bit location is a 1.

25

**Base Address :** This register is used to record the base address of the device. When reading register 10h, the returned values are 1 for bit 0 and 0 for bit 1, it means that the W99200F is mapped into I/O space. When reading register 14h, the returned values are "0000" for bit[3:0], it means that the W99200F is mapped to memory space. This memory space is used to read video FIFO data. When reading register 18h, the returned values are "0000" for bit[3:0], it means that the W99200F is mapped to read video FIFO data.

For example:

(1) I/O space:

- Step1: The host issues a configuration write command to PCI bridge and address is 0x10, data is 0xffffffff.

- Step 2: The host issues a configuration read command to PCI bridge and address is 0x10. W99200F will send data 0xfffffff1. It means W99200F needs a 16-byte IO space. (Please refer to PCI spec for detail.)

- Step 3: The host issues a configuration write command to PCI bridge and address is 0x10, data is , for example, 0x80000. (This address is allocated by OS and called as IO space base address.) Then W99200F will be mapped into IO space and its address is 0x80000 ~ 0x8000f.

Actually, W99200F is only mapped into 3 double-word IO space. They are, for example, 0x80000, 0x80004 and 0x80008. We call them as AIR, DPR and ODPR in sequence. We will detailedly describe them in the section "I/O Access Cycle".

(2) memory space:

- Step1: The host issues a configuration write command to PCI bridge and address is 0x14 (or 0x18), data is 0xffffffff.

- Step 2: The host issues a configuration read command to PCI bridge and address is 0x14 (or 0x18). W99200F will send data 0xfffff000. It means W99200F needs a 4K-byte memory space. (Please refer to PCI spec for detail.)

- Step 3: The host issues a configuration write command to PCI bridge and address is 0x14 (or 0x18), data is, for example, 0x2000000. (This address is allocated by OS and called as memory space base address.) Then W99200F will be mapped into memory space and its address is 0x2000000 ~ 0x2000fff.

We will detailedly describe it in the section "Target mode memory read cycle".

- **CardBus CIS Pointer :** This optional register is used by those devices that want to share silicon between CardBus and PCI. For W99200F, the returned value is 0 while reading this register.

- Subsystem Vendor ID and Subsystem ID : This is also a read only register. When reading these two register, the returned values are always zero.

- Expansion ROM Base Address : It is a read only register and the read value is always kept at zero.

- Cache Line Size : This register specifies the system cache line size in unit of 32-bits word. This register is set to 0 to ignore PCI cache support lines. At reset this field should be set to 0.

- Latency Timer : This register is readable/writeable register. After hardware reset, it is set to zero and the system BIOS must write an appropriate value to the register.

- **BIST** : The BIST(Built in self test) register is also read-only and the returned value is always zero for W99200F.

- Interrupt Line : This is a 8-bit register used to communicate interrupt line routing information. The register is read/write-able. The value in this register tells which input of the system interrupt controller the device's interrupt pin is connected to.

- Interrupt Pin : The interrupt pin register tells which interrupt pin the device uses. This register is read only. For the W99200F, the returned value would be 1.

- Min\_GNT : The value of this register specifies how long a burst period the device needs assuming a clock rate of 33 MHz. For the W99200F, this is a read-only register and the returned value is FFh.

- Max\_LAT : This register is used for specifying how often the device needs to gain access to the PCI bus. For W99200F, this is also a read-only register and the returned value is 01h.

26

| Bit Location | Description                                                                            |  |

|--------------|----------------------------------------------------------------------------------------|--|

| 0            | Controls a device's response to I/O space access. A value of 0 disables the device     |  |

|              | response. A value of 1 enables the response. This is a read/write bit and the          |  |

|              | default value is 0.                                                                    |  |

| 1            | Controls a device's response to memory space accesses. A value of 0 disables the       |  |

|              | device response. A value of 1 enables the response. This is a read/write bit and the   |  |

|              | default value is 0.                                                                    |  |

| 2            | Controls a device's ability to act as a master of the PCI bus. It is a read/write bit. |  |

|              | The default value is 0.                                                                |  |

| 3            | Controls the device's action on Special Cycle operation. This bit is read-only and     |  |

|              | its value is set to 0.                                                                 |  |

| 4            | Memory Write and Invalidate Enable. This bit is read-only. Its value is 0.             |  |

| 5            | VGA Palette Snoop. A read-only bits. A '0' is set to this bit.                         |  |

| 6            | This is a read only bit and the returned value is always 0. It means that the          |  |

|              | W99200F will not do the parity check.                                                  |  |

| 7            | This bit is read-only and fixed at zero. It means that the W99200F does not do         |  |

|              | address/data stepping.                                                                 |  |

| 8            | This is an enable bit for the SERR# driver. A 0 value disables the SERR# driver.       |  |

|              | A 1 value enables the SERR# driver. After hardware reset, this bit is fixed at 0.      |  |

| 9            | Fast Back-to-Back Enable. This is a read-only bit. The returned value is 0. It         |  |

|              | means that the W99200F doesn't do fast back-to-back transaction in master mode.        |  |

| 10 - 15      | Reserved                                                                               |  |

### **Table 7-1: Command Register Bits**

| Bit Location | Description                                                                          |  |  |  |

|--------------|--------------------------------------------------------------------------------------|--|--|--|

| 0 - 4        | Reserved                                                                             |  |  |  |

| 5            | This optional read-only bit is fixed at 0 to indicate that the W99200F is capable of |  |  |  |

|              | running at 33 MHz.                                                                   |  |  |  |

| 6            | This optional read-only bit is set to zero for the W99200F. It means the W99200F     |  |  |  |

|              | does not support User Definable Features.                                            |  |  |  |

| 7            | This is a read-only bit and returned value is 1. It means that the W99200F is        |  |  |  |

|              | capable of accepting the fast back-to-back transaction in bus target mode            |  |  |  |

| 8            | The bit is read only. The returned value is 0.                                       |  |  |  |

| 9 - 10       | DEVSEL timing. The two bits encode the timing of DEVSEL#. These bits are             |  |  |  |

|              | read only and indicates the slowest time that a device asserts DEVSEL# for any       |  |  |  |

|              | bus command except Configuration Read and Write. For W99200F, these bits are         |  |  |  |

|              | set to be 01b for medium timing.                                                     |  |  |  |

| 11           | Signaled Target Abort. This bit must be set by a target when it terminates a         |  |  |  |

|              | transaction with target-abort.                                                       |  |  |  |

| 12           | Receive Target Abort. While the W99200F operates as a bus master, this bit will      |  |  |  |

|              | be set whenever its transaction is terminated with target-abort.                     |  |  |  |

| 13           | Received Master Abort. If the W99200F acts as a bus master, this bit must be set     |  |  |  |

|              | whenever its transaction is terminated with master abort. It is readable/writeable.  |  |  |  |

| 14           | Signaled System Error. The returned value is always zero.                            |  |  |  |

| 15           | Detected Parity Error. This bit must be set by the device whenever it detects a      |  |  |  |

|              | parity error, even if parity handling is disabled.                                   |  |  |  |

# Table 7-2: Status Register Bits

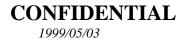

The W99200F is a target of the configuration command (read or write) only when its IDSEL pin is high and AD[1:0] are 00 during the address phase of the configuration command. Internal addressing of the 64-DWORD configuration space is done by AD[7:2], and C/BE[3:0]# indicates the bus command. This timings of configuration read and write command are shown in Figure 7-2 and Figure 7-3 respectively. The mark xxxx in IDSEL means an invalid state. The detail description of timing will be given in the description of timing of IO access.

Figure 7-2: PCI Configuration Read Timing

# Preliminary

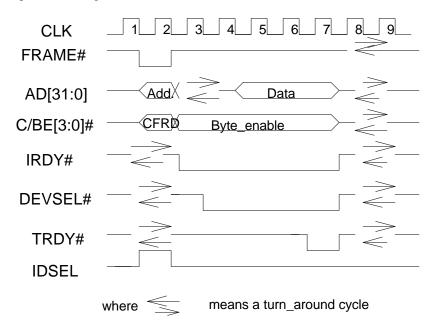

Figure 7-3: PCI Configuration Write Timing

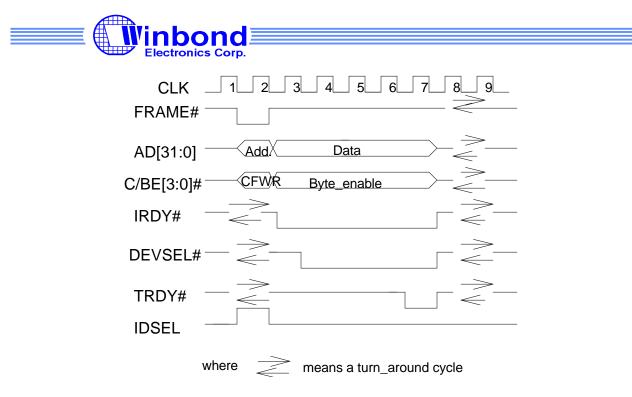

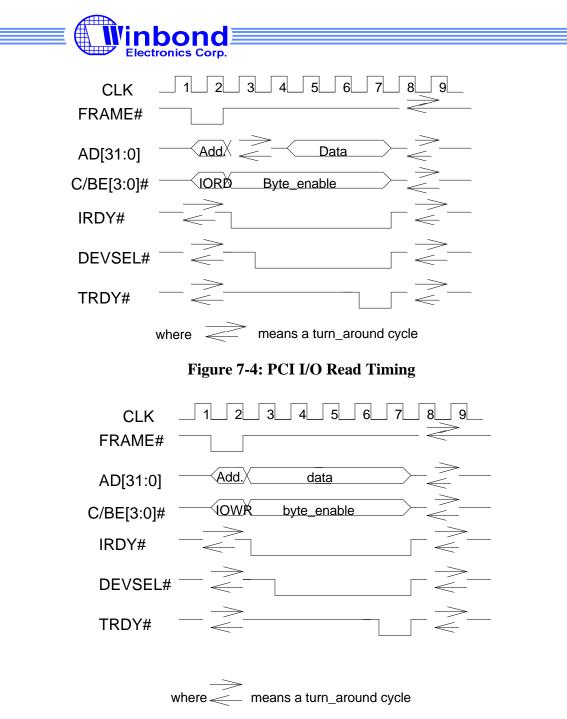

7.1.1.2 I/O Access Cycle:

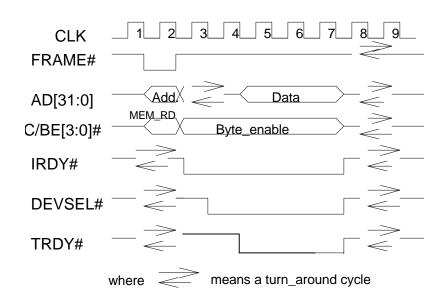

The host can access the internal control, status registers, local SDRAM by using a set of Address Index Port Register and Data Port Register. All the above access cycles are I/O-mapped access cycles. The timing diagrams of I/O mapped accessing are illustrated in Figure 7-4 and Figure 7-5 for I/O read and I/O write respectively. In Figure 7-4, a Read transaction starts with an address phase which occurs when FRAME# is asserted for the first time and it occurs on clock2 in this figure. FRAME# is deasserted on clock 3 to indicated that the current transaction is single mode. During address phase, AD[31:0] contain a valid address and C/BE[3:0]# contain a valid bus command. The first clock of data phase is clock 3. During data phase, C/BE[3:0]# indicate which byte lanes are involved in the current data phase. DEVSEL# is active on clock 4 to inform host that a device (W99200F) has been selected in this data transaction. The whole data transaction completes when data are transferred which occurs when both IRDY# and TRDY# are asserted on the same clock edge. In this figure, the data transfer completes on clock 7. While the data transfer is done, all signals including FRAME#, IRDY#,

TRDY#,DEVSEL# are all deasserted. The notation " — " in Figure 7-4 means a turnaround cycle which is necessary for all signal that may be driven by more than one agent. Figure 7-5 illustrates a Write transaction. The Write transaction is similar to a Read transaction except no turnaround cycle is required following the address phase in AD[31:0].

# Preliminary

#### Figure 7-5: PCI I/O Write Timing

#### 7.1.1.3 Target Mode Memory Read Cycle:

The host can read internal Vdata\_out FIFO by memory read cycles. The timing diagram of memory read cycle is illustrated in Figure 7-6. A read transaction starts with an address phase which occurs when FRAME# is asserted for the first time and it occurs on clock 2 in this figure. FRAME# is deasserted on clock 3 to indicated that the current transaction is single mode. During address phase, AD[31:0] contain a valid address and C/BE[3:0]# contain a valid bus command. The first clock of

data phase is clock 3. During data phase, C/BE[3:0]# indicate which byte lanes are involved in the current data phase. DEVSEL# is active on clock 4 to inform host that a device (W99200F) has been selected in this data transaction. The whole data transaction completes when data are transferred which occurs when both IRDY# and TRDY# are asserted on the same clock edge. In this figure, the data transfer completes on clock 5, 6 and 7. While the data transfer is done, all signals

including FRAME#, IRDY#, TRDY#, DEVSEL# are all deasserted. The notation ", in Figure 7-6 means a turnaround cycle which is necessary for all signals that may be driven by more than one agent.

#### Figure 7-6: PCI Target Mode Memory Read Timing

For example, suppose that the memory mapping space of W99200F is  $0x2000000 \sim 0x2000$ ff, the host can read the data from internal Vdata\_out register by the following procedure:

After initialization, while the host receives "FIFO ready" interrupt request, the host first reads the value of "Vthreshold" register. The host should read up to threshold level units of data from video Vdata\_out FIFO (or audio FIFO). The host issues the first memory read command, address = 0x2000000, to get the first data of Vdata\_out (or Audio\_out) register. Issuing the second memory read cycle, address = 0x2000004, to get the second data. And issuing the 3rd memory read cycle, address = 0x2000004, to get the second data. And issuing the 3rd memory read cycle, address = 0x2000008, to get the 3rd data, and so on. The host may also issue burst memory read command to read data from Vdata\_out (or Audio\_out) register. The burst length will be decided by PCI control chip (PC core logic chip). But it is equal or less to threshold level. When the memory address reaches up to 0x2000ffc, the host should issue the memory read cycle, address = 0x2000000, in the next time. Note that the maximal size of memory mapping space must be multiple of threshold level DWORD. That means some region of W99200F memory mapping space (it is fixed to 4K bytes.) may not be used by the host.

Note that PCI bridge doesn't support burst cycle to access memory mapping space II (Audio\_out register).

Actually, the target mode memory read cycles with address located at W99200F memory mapping space I will all be translated to FIFO\_RD# cycles in generic bus by PCI bridge. And the target mode memory read cycles with address located at W99200F memory mapping space II will all be translated to RD# cycles in generic bus and A[6:0]=0x67.

31

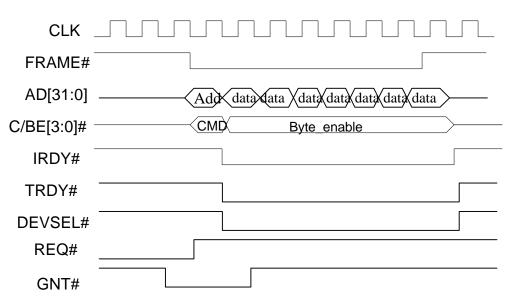

7.1.1.4 Master Mode Memory Write Cycle:

In 32-bit PCI bus, the input frames are sent to Host via PCI bus master mode. In PCI bus master mode, W99200F plays the role of a bus master and asserts the memory write command to output bitstream data from Vdata\_out FIFO in burst mode. The timing of this type of accessing is shown in Figure 7-7. In this mode, the W99200F asserts REQ# to request the ownership of bus to write the frame data to host. If the GNT# is detected active, it means that the request of bus ownership has been granted by the bus arbiter and the W99200F will pull FRAME# to low, deassert REQ#, put the address of target of current access on AD[31:0] and memory write command on C/BE[3:0]# to initiate the memory write bus transaction. IRDY# will be active at the rising at next cycle to indicates that the W99200F is ready to send the data and byte enable will also be put on C/BE[3:0]# to indicates which byte lane is desired simultaneously. The pointed target will receive the data while both TRDY# and IRDY# are low. Data transfer will be continued until FRAME# is driven to high to indicate that the last DWORD will be transferred at next cycle. Whole bus transaction will be completed when the last DWORD data is written.

#### Figure 7-7: PCI Memory Write Timing of Bus Master in Burst Mode

The procedure of master mode memory write cycle:

- 1. After initialization, the host programs BBSAR0, BBSAR1, BBS0 and BBS1 and sets BB\_RDY0=1. Then set BB\_RDY1=1.

- 2. The host sets MASTER\_EN=1.

- 3. If FIFO\_RDY =1, PCI bridge asserts REQ# to PCI bus.

- 4. While GNT# is low, FRAME# and IRDY# are high, PCI bridge issues master mode memory burst write command to PCI bus. Burst length is equal to threshold level. The address is equal to BBSAR0. This command will move the data from Vdata\_out FIFO to Buffer0 in the system main memory.

- 5. Goto step 3 and the address is increased 4\* threshold level, until Buffer0 is full.

- 6. While Buffer0 is full, PCI bridge automatically sets BB\_FULL0 "1", and BB\_RDY0 "0". And PCI bridge asserts INT# to the host.

- 7. At that time, if BB\_RDY1=1, PCI bridge starts to move the data from Vdata\_out FIFO to Buffer1.

32

- 8. In the mean time, the host responds INT# by reading BSTR. If the host finds BB\_FULL0 =1 and BB\_FULL1 =0, the host programs new BBSAR0 and BBS0. Then the host sets BB\_RDY0=1 and clears BB\_FULL0. The host starts to move out the data of the original Buffer0 to other storages, for example, hard disk.

- 9. While Buffer1 is full, PCI bridge automatically sets BB\_FULL1 "1", and BB\_RDY1 "0". And PCI bridge asserts INT# to the host.

- 10. At that time, if BB\_RDY0=1, PCI bridge starts to move the data from Vdata\_out FIFO to Buffer0.

- 11. In the mean time, the host responds INT# by reading BSTR. If the host finds BB\_FULL1 =1 and BB\_FULL0 =0, the host programs new BBSAR1 and BBS1. Then the host sets BB\_RDY1=1 and clears BB\_FULL1. The host starts to move out the data of the original Buffer1 to other storages, for example, hard disk.

- 12. Goto step 6.

7.1.1.5 I/O Registers

#### 7.1.1.5.1 IO Register Decoding

For the 32-bit PCI bus, based on the PCI Local Bus specification 2.1, the W99200F provides a set of configuration registers to achieve the purpose of total software initialization and configuration. By using these configuration registers, system will allocate proper resources to the W99200F, like I/O port base address and interrupt line, etc. The user can get these resource information by reading the corresponding configuration registers and using the I/O base address allocated by system BIOS as the base address of I/O register. The W99200F will decode the base address at the address phase of each IO-mapped bus transaction to determine whether to response or not.

#### 7.1.1.5.2 I/O Registers Mapping

There are three I/O registers which are DWORD addressable in a 32-bit PCI host bus configuration. The corresponding I/O addresses and their type are specified as follows:

(1) DWORD address configuration for PCI bus:

| Register Name | Address | Туре       |

|---------------|---------|------------|

| AIR           | IOAR    | read/write |

| DPR           | IOAR+4h | read/write |

| ODPR          | IOAR+8h | read       |

IOAR will be decoded in address phase of bus transaction to identify whether W99200F is the target of current bus transaction or not and the values, 04h, or 08h will be used to select which I/O port is accessed in current transaction. The content of IOAR is stored in the configuration register whose address is 10h in the configuration space.

#### Address Index Register (AIR)

| AIR[6:0]       |  |

|----------------|--|

| register index |  |

Address Index Register, AIR, is used to specify the index value of internal register. When PCI host access AIR, AIR[6:0] are equal to the data phase of AD[6:0], and AD[31:7] are not used.

#### Data Port Register (DPR)

CONFIDENTIAL 1999/05/03

33

| DPR                   |  |

|-----------------------|--|

| bit[31:0] or bit[7:0] |  |